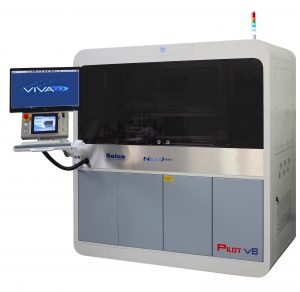

Die beste Lösung zur Automatisierung dieses langen Prozesses für das Reverse Engineering ist der Pilot V8 Next Series Tester von Seica. Die PCB-Zugänglichkeit auf beiden Seiten ist eine vorläufige und obligatorische Voraussetzung für die vollständige Neuerstellung der Netzliste, da nur so Verbindungen zwischen SMD-Komponenten auf gegenüberliegenden Seiten hergestellt werden können. Die vertikale Architektur ist die beste mechanische Dämpfung, da die Vibrationen der Platine nicht durch die Schwerkraft erhöht werden. Ausgefeilte, aber benutzerfreundliche Algorithmen reduzieren die Gesamtzahl der Tests drastisch und reduzieren die gesamte Rücklaufzeit und die Gesamtkosten. Die neu erstellten Daten können verwendet werden, um ein Testprogramm durch automatische Verfahren zu generieren.

1. BOARD ANALYSE

Dank mehrerer Inspektions- und Analysetechniken kann die VIVA-Software sowohl auf montierten als auch auf blanken Platinen betrieben werden.

Das Reverse Engineering kann einen destruktiven oder einen zerstörungsfreien Ansatz haben. Die erste Methode zerstört das Gerät während des Testvorgangs, während der zerstörungsfreie Prozess nach der Analyse die volle Funktionalität des zu testenden Geräts beibehält. Der Pilot V8 Next Series> -Tester von Seica verfügt über eine zerstörungsfreie Methode, obwohl die folgenden Ausnahmen berücksichtigt und gelöst werden müssen:

1) Mikrochips mit BGA-Gehäusen mit den Stiften unter der Komponente, da die Pads freigelegt werden müssen.

2) Komponenten ohne Zugänglichkeit.

3) Schutzbeschichtung, bei der es sich um einen dünnen Polymerfilm handelt, der auf eine Leiterplatte (PCB) aufgebracht wird.

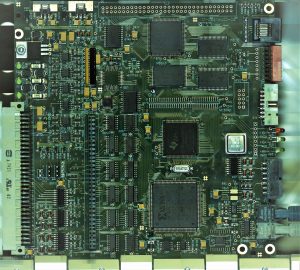

Das Ergebnis des Netlist-Autolearning-Verfahrens hängt von der tatsächlichen Zugänglichkeit der Sonden an den Testpunkten ab. Folgende Arten von elektronischen Karten können analysiert werden:

– Bare Board: Diese Bedingung ermöglicht ein vollständiges und zuverlässiges Lernen aller Netzlisten auf der Leiterplatte. Darüber hinaus ist die Überprüfung der gelernten Daten relativ einfach und schnell.

– Teilweise montierte Platine: Um die Zugänglichkeit zu verbessern und die nachfolgenden manuellen Vorgänge zu minimieren, wird empfohlen, diejenigen Komponenten zu entfernen, die den Zugang zu einigen Pads verhindern.

– Vollständig zusammengebaute Karte: In diesem Fall kann die eingeschränkte Zugänglichkeit zu den Pads die Ausführung eines manuellen Netzlistenlernens mit den in der VIVA-Software verfügbaren Tools erfordern.

2. AUTOLEARNING: DIGITALISIERUNG DES DUAL SIDE BOARD

Die CCD-Farbkameras, die auf jeder Seite eines Pilot V8 Flying Prober verfügbar sind, digitalisieren zwei detaillierte Bilder der Ober- und Unterseite der Platine. Seica hat mehrere manuelle und automatische Routinen entwickelt, die die XY-Standortkoordinaten mithilfe des integrierten AOI-Systems identifizieren. Es gibt vier Modi zum automatischen Lernen aller Punkte und Komponenten einer Karte: Manuell, Automatisch, Anschluss und Komponente. Diese Technik reproduziert das vollständige Layout und ist nützlich für die Datenverarbeitung und -analyse, entweder online (automatisches Lernen) im System oder offline (Digitalisierer) auf einem Remote-PC.

3. NETLIST LEARNING

Der erste Schritt besteht darin, mindestens einen GND-Punkt manuell zu identifizieren. Ebenso kann der Benutzer den VCC-Punkt bestimmen, wenn er für die Netzlistenanalyse nützlich ist. Sobald der Benutzer das GND-Signal klassifiziert hat, kann der „Netlist Learning“ -Prozess auf dem Flying Prober mit dem FNODE-Makro beginnen.

FNODE

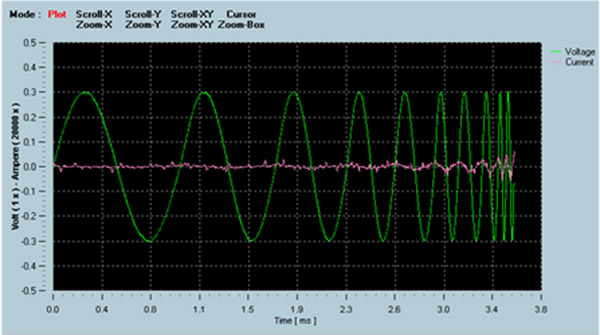

Seica verwendet ein proprietäres dynamisches Impedanzmessverfahren mit der Bezeichnung FNODE, das die Nettosignatur eines analogen Dipols erhält. Diese leistungsstarke Testmethode wird verwendet, um die dynamische Impedanz eines unbekannten Dipols zu messen, um alle Netze einer montierten Platine zu erkennen und zu trennen. Daraus ergibt sich eine geeignete Anzahl von Durchgangstests.

Da jeder Dipol des Prüflings unbekannt ist, wird ein „Auto-Learn“ der Goldenen Tafel verwendet, um das Verhalten des Dipols über einen weiten Frequenzbereich zu erfassen. Ein Signalgenerator legt einen Frequenzdurchlauf an Pin1 an, während Pin2 mit GND verbunden ist. In Grün die Spannung zwischen dem zu prüfenden Netz und Masse, in Magenta die aktuelle Signatur des Netzes. Die typische Eingangssignalamplitude beträgt 0,2 V, um unterhalb der PN-Übergangsschwelle zu liegen und nichtlineare Verzerrungen sowie Schutzmaßnahmen zu vermeiden (elektrische Isolierung der Netzumgebung, um eine Einzelmessung an einer einzelnen Komponente durchzuführen). Der FNODE misst den Strom, der in den Dipol fließt, und jeweils die Amplitude und die Phase für jedes Netz werden vom Testprogramm gespeichert. Der FNODE ist ein rein passives Messverfahren ohne Strom am Prüfling.

Die Vorteile von FNODE lassen sich leicht zusammenfassen:

– Es werden keine CAD-Daten benötigt und es ist kein manuelles Debuggen erforderlich

– Der automatische Lernprozess ist vollautomatisch und erzeugt einen vollständigen Kurzschlusstest mit einer höheren Fehlerabdeckung als der herkömmliche Adjazenztest. Darüber hinaus können viele In-Circuit-Messungen vermieden werden, ohne die Testabdeckung zu verringern. Bei diesem Verfahren wird ein DSP-basiertes Multifunktionsinstrument (Digital Signal Processor) verwendet, das die erzeugten und gemessenen Signale digitalisiert. Die erfassten Daten ermöglichen die nahezu gleichzeitige Ausführung mehrerer Hochgeschwindigkeitstests, da alle Testmodelle „hardwareemuliert“ sind, was den Testdurchsatz erheblich erhöht.

KONTINUITÄTS-MAKRO

Wenn zwei oder mehr Netze dieselbe aktuelle Signatur haben, besteht der nächste Schritt darin, den Kontinuitätstest auszuführen. Das Hauptziel des CONTINUITY-Makros, das für die Arbeit in Sätzen von jeweils 1000 Tests optimiert wurde, besteht darin, die zu demselben Netz gehörenden Testfelder zu gruppieren. Dieses Verfahren ist auch in der Lage, die mit niedriger Impedanz verbundenen Signale (z. B. Induktivitäten, Widerstände bei 0 Ohm…) als separate Netze zu erfassen, wenn sie zu zweipoligen Komponenten gehören, die regelmäßig in der Edit Board der VIVA-Software für grafische Umgebungen deklariert werden.

PWMON

Zu diesem Zeitpunkt ist es notwendig, die Signaturen / Funktionen der digitalen Komponenten zu erfassen. Sobald die GND- und VCC-Eingänge identifiziert wurden, wird der Prüfling eingeschaltet, um den Power Monitor (PWMON) auszuführen. Es ist möglich, den Strom zu messen, der zur Erzeugung von logisch 0 oder logisch 1 an jedem Knoten (Eingangspin einer digitalen Komponente) benötigt wird. Auf diese Weise wird der Schwellenwert gelernt und das System kann einen möglichen Fehler in einem Netz erkennen. Bei dieser Methode ist ein „goldenes Brett“ nicht erforderlich, wird jedoch dringend empfohlen.

Die Vorteile von PWMON lassen sich wie folgt zusammenfassen:

– Es ist eine vektorlose Methode, um ICs im eingeschalteten Zustand zu testen.

– Es kann ohne CAD-Daten generiert werden.

– Es sind keine manuellen Vorgänge erforderlich, da es sich um ein vollautomatisches Verfahren handelt und unabhängig von den Initialisierungsbedingungen des Prüflings ist (wenn der Prüfling eingeschaltet ist).

4. TESTPROGRAMM-ERSTELLUNG

Nach Abschluss des Netzlisten-Lernverfahrens und der möglichen manuellen Korrektur-Verbindung einiger Netze können die Ergebnisse genutzt werden, um ein Testprogramm für Reparaturaktivitäten zu generieren und/oder die Daten bereitzustellen, die für das Reverse Engineering der Baugruppenschaltpläne benötigt werden.