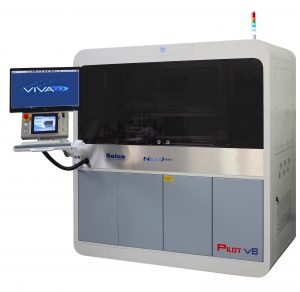

La soluzione migliore per automatizzare questo lungo processo per il Reverse Engineering è il tester Pilot V8 Next Series di Seica. L’accessibilità del PCB su entrambi i lati è una condizione preliminare e obbligatoria per ricostruire completamente la netlist perché questo è l’unico modo per apprendere le connessioni tra componenti SMD su lati opposti. L’architettura verticale è il migliore smorzamento meccanico perché le vibrazioni della tavola non sono aumentate dalla forza di gravità. Gli algoritmi sofisticati ma di facile utilizzo riducono drasticamente la quantità totale di test, riducendo il tempo e i costi totali inversi. I dati ricostruiti sono pronti per essere utilizzati per generare un programma di test con procedure automatiche.

1. BOARD ANALYSIS

Grazie a molteplici tecniche di ispezione e analisi, il software VIVA può funzionare sia su schede montate che nude. Il Reverse Engineering può avere un approccio distruttivo o non distruttivo. Il primo metodo distruggerà il dispositivo durante la procedura di test, mentre il processo non distruttivo mantiene la piena funzionalità del dispositivo sottoposto a test dopo l’analisi.

Il tester Pilot V8 Next Series> di Seica presenta un metodo non distruttivo, anche se le seguenti eccezioni devono essere prese in considerazione e risolte:

1) Microchip con pacchetti BGA con i pin sotto il componente, poiché è necessario esporre i pad.

2) Componenti senza accessibilità.

3) Rivestimento protettivo che è un sottile film polimetrico applicato a un printed circuit board (PCB). Il risultato della procedura di auto-learning della netlist dipende dalla reale accessibilità delle sonde sui punti di test.

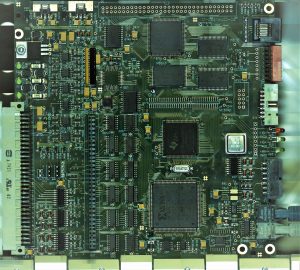

È possibile analizzare i seguenti tipi di schede elettroniche:

-Bareboard: questa condizione fornisce un apprendimento completo e affidabile di tutte le netlist presenti sul PCB. Inoltre, il controllo dei dati appresi è relativamente facile e veloce.

-Partially mounted board: per migliorare l’accessibilità e minimizzare le successive operazioni manuali, si consiglia di rimuovere quei componenti che impediscono l’accesso ad alcuni pad.

-Fully assembled board: in questo caso, l’accessibilità limitata ai pad può richiedere l’esecuzione dell’apprendimento netlist manuale utilizzando gli strumenti dedicati disponibili nel software VIVA.

2. AUTOLEARNING: DUAL SIDE BOARD DIGITALIZING

La soluzione migliore per automatizzare questo lungo processo per il Reverse Engineering è il tester Pilot V8 Next Series di Seica. L’accessibilità del PCB su entrambi i lati è una condizione preliminare e obbligatoria per ricostruire completamente la netlist perché questo è l’unico modo per apprendere le connessioni tra componenti SMD su lati opposti. L’architettura verticale è il migliore smorzamento meccanico perché le vibrazioni della tavola non sono aumentate dalla forza di gravità. Gli algoritmi sofisticati ma di facile utilizzo riducono drasticamente la quantità totale di test, riducendo il tempo e i costi totali inversi. I dati ricostruiti sono pronti per essere utilizzati per generare un programma di test con procedure automatiche.

1. BOARD ANALYSIS

Grazie a molteplici tecniche di ispezione e analisi, il software VIVA può funzionare sia su schede montate che nude. Il Reverse Engineering può avere un approccio distruttivo o non distruttivo. Il primo metodo distruggerà il dispositivo durante la procedura di test, mentre il processo non distruttivo mantiene la piena funzionalità del dispositivo sottoposto a test dopo l’analisi.

Il tester Pilot V8 Next Series> di Seica presenta un metodo non distruttivo, anche se le seguenti eccezioni devono essere prese in considerazione e risolte:

1) Microchip con pacchetti BGA con i pin sotto il componente, poiché è necessario esporre i pad.

2) Componenti senza accessibilità.

3) Rivestimento protettivo che è un sottile film polimetrico applicato a un printed circuit board (PCB). Il risultato della procedura di auto-learning della netlist dipende dalla reale accessibilità delle sonde sui punti di test.

È possibile analizzare i seguenti tipi di schede elettroniche:

-Bareboard: questa condizione fornisce un apprendimento completo e affidabile di tutte le netlist presenti sul PCB. Inoltre, il controllo dei dati appresi è relativamente facile e veloce.

-Partially mounted board: per migliorare l’accessibilità e minimizzare le successive operazioni manuali, si consiglia di rimuovere quei componenti che impediscono l’accesso ad alcuni pad.

-Fully assembled board: in questo caso, l’accessibilità limitata ai pad può richiedere l’esecuzione dell’apprendimento netlist manuale utilizzando gli strumenti dedicati disponibili nel software VIVA.

2. AUTOLEARNING: DUAL SIDE BOARD DIGITALIZING

Le telecamere a colori CCD, disponibili su ciascuno lato di un Pilot V8 Flying Prober, digitalizzano due immagini dettagliate sei lati superiore e inferiore della scheda. Seica ha sviluppato diverse routine manuali e automatiche che identificano le coordinate della posizione XY utilizzando il sistema AOI integrato. Esistono quattro modalità per l’autoapprendimento di tutti i punti e componenti di una scheda: Manual, Automatic, Connector and Component. Questa tecnica riproduce il layout completo ed è utile per l’elaborazione e l’analisi dei dati, sia online (auto-learn) nel sistema che offline (digitalizzatore)su un PC remoto.

3.NETLIST LEARNING

Il primo step è di identificare manualmente almeno un punto GND. Allo stesso modo, l’utente può determinare il punto VCC se è utile per l’analisi netlist. Una volta che l’utente ha classificato il segnale GND, il processo “netlist learning” sul Flying Prober può iniziare con la macro FNODE.

FNODE

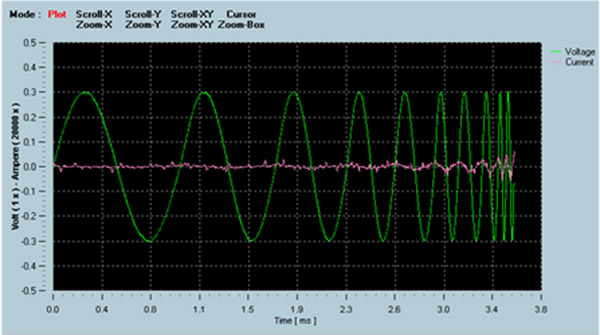

Seica utilizza un metodo di misurazione dell’impedenza dinamica proprietaria designato come FNODE, che acquisisce la firma di un dipolo analogico. Questo potente metodo di prova viene utilizzato per misurare l’impedenza dinamica di un dipolo sconosciuto per riconoscere e separare tutte le reti di una scheda montata. Da ciò, crea un numero adeguato di test di continuità. Poiché ciascun dipolo dell’UUT non è noto, viene utilizzato un “auto-learn” della scheda aurea per acquisire il comportamento del dipolo su un ampio intervallo di frequenze. Un generatore di segnali applica uno sweep di frequenza al pin1 mentre pin 2 e collegato a GND. In verde, la tensione applicata tra la rete sotto test e terra, in magenta la firma della rete. L’ampiezza tipica del segnale di ingresso è di 0,2V per essere al di sotto della soglia di transizione P-N e per evitare distorsioni non lineari e anche la protezione (isolando elettricamente l’ambiente di rete per eseguire una misura individuale su in singolo componente). FNODE misura la corrente che scorre nel dipolo e, in ogni caso, l’ampiezza e la frase di ciascuna rete sono memorizzate dal programma di test. FNODE è una procedura di misurazione puramente passiva, senza alimentazione sull’UUT.

I vantaggi di FNODE sono facilmente riassunti:

-Non ha bisogno di dati CAD e non è necessario il debug manuale.

-Il processo di auto-learn è completamente automatico e crea un cortocircuito completo con una copertura di errore superiore rispetto al tradizionale test di adiacenza. Inoltre, è possibile evitare molte misurazioni in

-Circuit senza ridurre la copertura del test. Questa procedura utilizza uno strumento multifunzione bassato su DSP (Digital Signal Processor), che digitalizza i segnali generati e misurati. I dati acquisiti consentono l’esecuzione quasi simultanea di più test ad alta velocità, poiché tutti i modelli di test sono “emulati dall’hardware”, aumentando sostanzialmente throughput del test.

Le telecamere a colori CCD, disponibili su ciascuno lato di un Pilot V8 Flying Prober, digitalizzano due immagini dettagliate sei lati superiore e inferiore della scheda. Seica ha sviluppato diverse routine manuali e automatiche che identificano le coordinate della posizione XY utilizzando il sistema AOI integrato. Esistono quattro modalità per l’autoapprendimento di tutti i punti e componenti di una scheda: Manual, Automatic, Connector and Component. Questa tecnica riproduce il layout completo ed è utile per l’elaborazione e l’analisi dei dati, sia online (auto-learn) nel sistema che offline (digitalizzatore)su un PC remoto.

3.NETLIST LEARNING

Il primo step è di identificare manualmente almeno un punto GND. Allo stesso modo, l’utente può determinare il punto VCC se è utile per l’analisi netlist. Una volta che l’utente ha classificato il segnale GND, il processo “netlist learning” sul Flying Prober può iniziare con la macro FNODE.

FNODE

Seica utilizza un metodo di misurazione dell’impedenza dinamica proprietaria designato come FNODE, che acquisisce la firma di un dipolo analogico. Questo potente metodo di prova viene utilizzato per misurare l’impedenza dinamica di un dipolo sconosciuto per riconoscere e separare tutte le reti di una scheda montata. Da ciò, crea un numero adeguato di test di continuità. Poiché ciascun dipolo dell’UUT non è noto, viene utilizzato un “auto-learn” della scheda aurea per acquisire il comportamento del dipolo su un ampio intervallo di frequenze. Un generatore di segnali applica uno sweep di frequenza al pin1 mentre pin 2 e collegato a GND. In verde, la tensione applicata tra la rete sotto test e terra, in magenta la firma della rete. L’ampiezza tipica del segnale di ingresso è di 0,2V per essere al di sotto della soglia di transizione P-N e per evitare distorsioni non lineari e anche la protezione (isolando elettricamente l’ambiente di rete per eseguire una misura individuale su in singolo componente). FNODE misura la corrente che scorre nel dipolo e, in ogni caso, l’ampiezza e la frase di ciascuna rete sono memorizzate dal programma di test. FNODE è una procedura di misurazione puramente passiva, senza alimentazione sull’UUT.

I vantaggi di FNODE sono facilmente riassunti:

-Non ha bisogno di dati CAD e non è necessario il debug manuale.

-Il processo di auto-learn è completamente automatico e crea un cortocircuito completo con una copertura di errore superiore rispetto al tradizionale test di adiacenza. Inoltre, è possibile evitare molte misurazioni in

-Circuit senza ridurre la copertura del test. Questa procedura utilizza uno strumento multifunzione bassato su DSP (Digital Signal Processor), che digitalizza i segnali generati e misurati. I dati acquisiti consentono l’esecuzione quasi simultanea di più test ad alta velocità, poiché tutti i modelli di test sono “emulati dall’hardware”, aumentando sostanzialmente throughput del test.

CONTINUITY MACRO

Se due o più reti hanno la stessa firma corrente, il passo successivo è eseguire il test di continuità. L’obiettivo principale della macro Continuity, ottimizzato per lavorare insiemedi 1000 test ciascuno, è raggruppare i pad di test appartenenti alla stessa rete. Questa procedura è anche in grado di rilevare come reti separate i segnali collegati a bassa impedenza (ad esempio induttori, resistenze a 0 Ohm) quando appartengono a componenti a due pin regolarmente dichiarati nell’ambiente grafico Edit Board del software VIVA.

PWMON

A questo punto, è necessario acquisire le firme/funzioni dei componenti digitali. Una volta identificati gli ingressi GND e VCC, l’UUT viene acceso per eseguire il Power Monitor (PWMON). È possibile misurare la corrente necessaria per produrre la logica 0 o la logica 1 su ciascun (pin di ingresso di un componente digitale). In questo modo, la soglia viene appresa e il sistema può riconoscere un possibile errore su una rete. Usando questo metodo, una “tavola dorata” non è necessaria ma fortemente raccomandata.

I vantaggi di PWMON sono riassunti come segue:

-È un metodo vettoriale per testare i circuiti integrati in condizioni di accensione.

-Può essere generato senza dati CAD.

-Non richiede operazioni manuali, poiché è una procedura completamente automatica ed è indipendente dalle condizioni di inizializzazione dell’UUT (quando l’UUT è acceso).

4. TEST PROGRAM CREATION

Una volta che la procedura di apprendimento della netlist è stata completata, insieme all’eventuale collegamento manuale di alcune reti, il gusto può essere impiegato per creare un programma di test ai fini dell’attività di riparazione e/o creare i dati da utilizzare per ricostruire gli schemi della scheda.

CONTINUITY MACRO

Se due o più reti hanno la stessa firma corrente, il passo successivo è eseguire il test di continuità. L’obiettivo principale della macro Continuity, ottimizzato per lavorare insiemedi 1000 test ciascuno, è raggruppare i pad di test appartenenti alla stessa rete. Questa procedura è anche in grado di rilevare come reti separate i segnali collegati a bassa impedenza (ad esempio induttori, resistenze a 0 Ohm) quando appartengono a componenti a due pin regolarmente dichiarati nell’ambiente grafico Edit Board del software VIVA.

PWMON

A questo punto, è necessario acquisire le firme/funzioni dei componenti digitali. Una volta identificati gli ingressi GND e VCC, l’UUT viene acceso per eseguire il Power Monitor (PWMON). È possibile misurare la corrente necessaria per produrre la logica 0 o la logica 1 su ciascun (pin di ingresso di un componente digitale). In questo modo, la soglia viene appresa e il sistema può riconoscere un possibile errore su una rete. Usando questo metodo, una “tavola dorata” non è necessaria ma fortemente raccomandata.

I vantaggi di PWMON sono riassunti come segue:

-È un metodo vettoriale per testare i circuiti integrati in condizioni di accensione.

-Può essere generato senza dati CAD.

-Non richiede operazioni manuali, poiché è una procedura completamente automatica ed è indipendente dalle condizioni di inizializzazione dell’UUT (quando l’UUT è acceso).

4. TEST PROGRAM CREATION

Una volta che la procedura di apprendimento della netlist è stata completata, insieme all’eventuale collegamento manuale di alcune reti, il gusto può essere impiegato per creare un programma di test ai fini dell’attività di riparazione e/o creare i dati da utilizzare per ricostruire gli schemi della scheda.